Mixed-signal Integrated circuit design

了解ADC、DAC的架構。從最基礎的sample and hold、Switched-capacitor circuits、Nyquist-rate D/A Converters到後面的實際應用,讓我對於video decoder的構造原理更有感覺。

16bit ADC

這裏使用pipeline ADC架構來符合高速且高解析的要求,pipeline ADC裡面分成數個小的sub-ADC來個別處理N個bit資料,當地一階處理完Nbit資料之後,會把餘數訊號放大之後送到下一階來處理。16bit 20MSPS ADC使用4階pipeline架構分別是5-4-4-4bit, 第一階使用5 bit flash ADC來符合高解析且高正確的要求,第三階與第四階裡面藉由在快閃式類比數位轉換器增加兩個額外的比較器與電容,所以可以省略error correction的電路。

9-bit DAC

這設計9bit ADC並且可以拆開成為5-4bit分別使用

結論

用這樣的架構,可以組成高速且高解析度類比數位轉換,解析度16bits, power supply 3v, sampling rate 20MSPS, power consumption 300mW, DNL +1.38~-0.92LSB, INL +6.7~-16.6LSB, PGA 1~6.25V/V.

針對各種ADC架構討論

Flash ADC

在各種高速類比數位轉換器架構中,以快閃類比數位轉換器為最基本。且速度也是最快。電路架構主要由電阻串、比較器及編碼器所組成。動作原理是利用電阻串的方式,將參考電壓分成若干臨界值連接至比較器,在與輸入訊號金行比較動作。而比較器的輸出為一thermometer code,再經過編碼之後可以得到一比數位資料。由於快閃類比數位轉換器的原理是採用並行方式來處理,所以他只需要依個時序週期,即可比較出輸入訊號是落再參考電壓的那一個區間,也因此具有高速轉換的優點。但是快閃式架構所設計的類比數位轉換器,必須使用大量的比較器,以一個具有N位元的類比數位轉換器為例,要使用2^N-1個比較器,當解析度越高時,比較器的數量也會次方增加,不但增加電路的消耗功率,也增加晶片的面積。所以一般快閃式類比數位轉換器通常不會超過8位元。

Two-step Flash ADC

由於Flash ADC使用的比較器相當多,對於增加轉換器解析度是一個相當不利的缺點。而用兩段為架構的ADC,可以有效降低在Flash ADC中比較器數量的問題。Two-step Flash ADC可分為兩級,每一級的部份包含的一個Flash ADC。其轉換分成兩個架構,第一階段時,第一級快閃式類比數位轉換器來處理輸入數位資料的最高位元,再經由一個數位類比轉換器將前一級的數位訊號在轉換成類比訊後之後,與來源相減,在把相減之後產生的餘數送到第二級的快閃式類比數位轉換器,第二及轉換器把類比訊號換轉換成LSB數位訊號。雖然轉換過程分成兩個步驟來完成,也比快閃架構的類比數位轉換器來的慢,但是在比較器的數量上,卻可以大幅的降低,在較高解析度的轉換器上,可以這樣來應用。以8位元轉換器來說,快閃式架構需要255個比較器,但是兩階段快閃式架構,只需要32個。因此兩階段架構可以有效降低比較器的數量,減少面積,降低功率消耗。

Pipeline ADC

管線式類比數位轉換器架構可以說是兩階段快閃式類比轉換器的延伸。主要的差別在於管線式的架構是將整個訊號的轉換過程細分成更多階段來完成,可以降低比較器的精確度要求,而比較器的精確度的要求及功率的消耗比其他高速ADC降低許多。每個階段主要包含了取樣保持電路、sub ADC、Gain stage ampler、餘數放大器。其中轉換原理為輸入訊號經由一個取樣保持電路,獲得一個直流準位,然後經由sub ADC轉換成數位職,再將此轉換後的數位職輸入移位暫存器,再經由DAC轉換成相對應的類比值,接著將取樣保持電路所獲得的準位在減去DAC轉換成相對應的類比值,產生餘數之後,再經過增益級將此餘數放大至下一階段,以此重複。最後經由錯誤校正電路,將所以產生的數位碼合併成一組N位元的數位資料輸出。但是這樣的電路會有延遲的問題。

Tie-interleave Parallel ADC

分時並行類比數位轉換器。若要達到更高轉換速度的類比數位轉換器,目前可以變通的方式是採用分時並行類比數位轉換器架構,主要動作原理是利用不同向位的時序訊號,控制各個通道的類比數位轉換器。輸入訊號經由相位0的控制去樣保持電路取樣之後,將訊號分別送進相位1~4的控制的取樣保持店戶,再由各個通道之內的類比數位轉換器進行轉換,每個通道在週期結束之前,會得到一筆資料,最後經由多輸出端的多工器解出各個通道轉換完成之後的數位資料,假如每個通道有40MHz,四個通道相當於可以處理160M的取樣頻率。但是相對的,晶片的面積與功率消耗也成比例增加,還有匹配性的問題、相位偏移、偏移誤差。

下面是我閱讀的幾篇混波積體電路相關文章

主要資料

1) A CMOS 16-bit 20MSPS Analog front end for scanner/MFP Application.

By Seung-Bin You, Jae-Whui Kim, Suki Kim. IEEE senior Member

IEEE Transactions on Consumer Electronics, Vol 49, No.3, August 2003.

2) Design of high-speed Analog-to-digital converter Base-on pipeline architecture

次要資料

3) Selecting an Analog Front-End for Imaging Applications

By Kevin Buckley, Analog Device.

前言

這篇文章使用16-bit AFE for CCD/CIS scanner and multi-function peripheral (MFP) ,使用3個channel 的高解析度雙取樣(correlated double sampler, CDS)、一個PGA(programmable gain amplifier)、一個參考電壓。這篇文章使用三星Samsung 0.35um CMOS 製程。晶片面積8mm,在3V電源供應之下功率消耗300mW。在CDS-PGA-ADC的通道傳輸之間,沒有missing code,且DNL在+1.3~-0.92LSB, INL在+6.7~-16.6LSB。

CCD、CIS目前再消費性電子已經是非常實用且受歡迎的產品,因此人們更需要更高解析度的AFE,但是大部分12~14bit接析度AFE只有在5V,15MSPS。這篇論文會提出16bit 20MSPS在3V且低功率消耗的AFE。第一,需要全差動的設計來降低雜訊的干擾同時能夠符合高動態訊號輸出;第二,在CDS的輸出訊號要注意在black level的校正位準;第三,每個獨立的PGA必要能夠提供給取樣電路足夠的最大輸入訊號;第四,低成本的ADC;最後需要一個DAC來提供black level offsets.

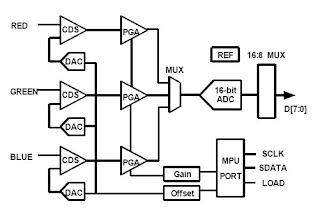

System design.

下面的圖在說明16bit的輸出是利用兩個8bit循環來取得。使用三條串列控制線,提供增益控制、black level control。這個圖的輸入分別來自訊號的RGB,當RGB訊號進入之後馬上進行CDS取樣。經過CDS後的輸出訊號會經過PGA的訊號放大到能夠符合ADC取樣的最大範圍,以確保是在ADC最大解析度下面的類比數位轉換。

主要資料

1) A CMOS 16-bit 20MSPS Analog front end for scanner/MFP Application.

By Seung-Bin You, Jae-Whui Kim, Suki Kim. IEEE senior Member

IEEE Transactions on Consumer Electronics, Vol 49, No.3, August 2003.

2) Design of high-speed Analog-to-digital converter Base-on pipeline architecture

次要資料

3) Selecting an Analog Front-End for Imaging Applications

By Kevin Buckley, Analog Device.

前言

這篇文章使用16-bit AFE for CCD/CIS scanner and multi-function peripheral (MFP) ,使用3個channel 的高解析度雙取樣(correlated double sampler, CDS)、一個PGA(programmable gain amplifier)、一個參考電壓。這篇文章使用三星Samsung 0.35um CMOS 製程。晶片面積8mm,在3V電源供應之下功率消耗300mW。在CDS-PGA-ADC的通道傳輸之間,沒有missing code,且DNL在+1.3~-0.92LSB, INL在+6.7~-16.6LSB。

CCD、CIS目前再消費性電子已經是非常實用且受歡迎的產品,因此人們更需要更高解析度的AFE,但是大部分12~14bit接析度AFE只有在5V,15MSPS。這篇論文會提出16bit 20MSPS在3V且低功率消耗的AFE。第一,需要全差動的設計來降低雜訊的干擾同時能夠符合高動態訊號輸出;第二,在CDS的輸出訊號要注意在black level的校正位準;第三,每個獨立的PGA必要能夠提供給取樣電路足夠的最大輸入訊號;第四,低成本的ADC;最後需要一個DAC來提供black level offsets.

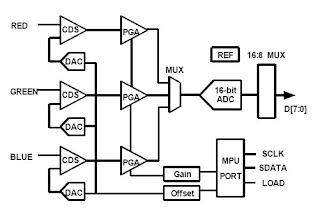

System design.

下面的圖在說明16bit的輸出是利用兩個8bit循環來取得。使用三條串列控制線,提供增益控制、black level control。這個圖的輸入分別來自訊號的RGB,當RGB訊號進入之後馬上進行CDS取樣。經過CDS後的輸出訊號會經過PGA的訊號放大到能夠符合ADC取樣的最大範圍,以確保是在ADC最大解析度下面的類比數位轉換。

CDS (correlated double sampler)

CDS架構利用兩個SHA進行取樣且可以消除OP的offset voltage,如果輸入訊號是CCD,那需要經過兩道CDS分別取出參考訊號與RGB訊號,若是CIS直接用CDS取出RGB訊號。

CDS架構利用兩個SHA進行取樣且可以消除OP的offset voltage,如果輸入訊號是CCD,那需要經過兩道CDS分別取出參考訊號與RGB訊號,若是CIS直接用CDS取出RGB訊號。

PGA (programmable gain amplifier)

PGA接受CDS取樣所傳的RBG訊號之後,依照外部MCU或DSP所傳回的資料,在除了在back level訊號之外,將衰減的訊號放大。

CDS架構利用兩個SHA進行取樣且可以消除OP的offset voltage,如果輸入訊號是CCD,那需要經過兩道CDS分別取出參考訊號與RGB訊號,若是CIS直接用CDS取出RGB訊號。

CDS架構利用兩個SHA進行取樣且可以消除OP的offset voltage,如果輸入訊號是CCD,那需要經過兩道CDS分別取出參考訊號與RGB訊號,若是CIS直接用CDS取出RGB訊號。PGA (programmable gain amplifier)

PGA接受CDS取樣所傳的RBG訊號之後,依照外部MCU或DSP所傳回的資料,在除了在back level訊號之外,將衰減的訊號放大。

16bit ADC

這裏使用pipeline ADC架構來符合高速且高解析的要求,pipeline ADC裡面分成數個小的sub-ADC來個別處理N個bit資料,當地一階處理完Nbit資料之後,會把餘數訊號放大之後送到下一階來處理。16bit 20MSPS ADC使用4階pipeline架構分別是5-4-4-4bit, 第一階使用5 bit flash ADC來符合高解析且高正確的要求,第三階與第四階裡面藉由在快閃式類比數位轉換器增加兩個額外的比較器與電容,所以可以省略error correction的電路。

9-bit DAC

這設計9bit ADC並且可以拆開成為5-4bit分別使用

結論

用這樣的架構,可以組成高速且高解析度類比數位轉換,解析度16bits, power supply 3v, sampling rate 20MSPS, power consumption 300mW, DNL +1.38~-0.92LSB, INL +6.7~-16.6LSB, PGA 1~6.25V/V.

針對各種ADC架構討論

Flash ADC

在各種高速類比數位轉換器架構中,以快閃類比數位轉換器為最基本。且速度也是最快。電路架構主要由電阻串、比較器及編碼器所組成。動作原理是利用電阻串的方式,將參考電壓分成若干臨界值連接至比較器,在與輸入訊號金行比較動作。而比較器的輸出為一thermometer code,再經過編碼之後可以得到一比數位資料。由於快閃類比數位轉換器的原理是採用並行方式來處理,所以他只需要依個時序週期,即可比較出輸入訊號是落再參考電壓的那一個區間,也因此具有高速轉換的優點。但是快閃式架構所設計的類比數位轉換器,必須使用大量的比較器,以一個具有N位元的類比數位轉換器為例,要使用2^N-1個比較器,當解析度越高時,比較器的數量也會次方增加,不但增加電路的消耗功率,也增加晶片的面積。所以一般快閃式類比數位轉換器通常不會超過8位元。

Two-step Flash ADC

由於Flash ADC使用的比較器相當多,對於增加轉換器解析度是一個相當不利的缺點。而用兩段為架構的ADC,可以有效降低在Flash ADC中比較器數量的問題。Two-step Flash ADC可分為兩級,每一級的部份包含的一個Flash ADC。其轉換分成兩個架構,第一階段時,第一級快閃式類比數位轉換器來處理輸入數位資料的最高位元,再經由一個數位類比轉換器將前一級的數位訊號在轉換成類比訊後之後,與來源相減,在把相減之後產生的餘數送到第二級的快閃式類比數位轉換器,第二及轉換器把類比訊號換轉換成LSB數位訊號。雖然轉換過程分成兩個步驟來完成,也比快閃架構的類比數位轉換器來的慢,但是在比較器的數量上,卻可以大幅的降低,在較高解析度的轉換器上,可以這樣來應用。以8位元轉換器來說,快閃式架構需要255個比較器,但是兩階段快閃式架構,只需要32個。因此兩階段架構可以有效降低比較器的數量,減少面積,降低功率消耗。

Pipeline ADC

管線式類比數位轉換器架構可以說是兩階段快閃式類比轉換器的延伸。主要的差別在於管線式的架構是將整個訊號的轉換過程細分成更多階段來完成,可以降低比較器的精確度要求,而比較器的精確度的要求及功率的消耗比其他高速ADC降低許多。每個階段主要包含了取樣保持電路、sub ADC、Gain stage ampler、餘數放大器。其中轉換原理為輸入訊號經由一個取樣保持電路,獲得一個直流準位,然後經由sub ADC轉換成數位職,再將此轉換後的數位職輸入移位暫存器,再經由DAC轉換成相對應的類比值,接著將取樣保持電路所獲得的準位在減去DAC轉換成相對應的類比值,產生餘數之後,再經過增益級將此餘數放大至下一階段,以此重複。最後經由錯誤校正電路,將所以產生的數位碼合併成一組N位元的數位資料輸出。但是這樣的電路會有延遲的問題。

Tie-interleave Parallel ADC

分時並行類比數位轉換器。若要達到更高轉換速度的類比數位轉換器,目前可以變通的方式是採用分時並行類比數位轉換器架構,主要動作原理是利用不同向位的時序訊號,控制各個通道的類比數位轉換器。輸入訊號經由相位0的控制去樣保持電路取樣之後,將訊號分別送進相位1~4的控制的取樣保持店戶,再由各個通道之內的類比數位轉換器進行轉換,每個通道在週期結束之前,會得到一筆資料,最後經由多輸出端的多工器解出各個通道轉換完成之後的數位資料,假如每個通道有40MHz,四個通道相當於可以處理160M的取樣頻率。但是相對的,晶片的面積與功率消耗也成比例增加,還有匹配性的問題、相位偏移、偏移誤差。

關鍵字: Mixed-signal、混波、ADC、DAC

4in1 video decoder for security and surveillance: Alogics、Techwell、Nextchip、TI、Conexant....

留言